# 800 Gb/s DR8 OSFP 500m Optical Transceiver

## **OSFP Series**

- Dual MPO-12 connector

- Support multi-rate operation

- Single 3.3V Power Supply

- Power consumption < 16W</p>

- Safety Certification:TUV/UL/FDA\*1

- PIN and TIA array on the receiver side

- EML 1310nm transmitter

- RoHS compliant

Ascent's OSFP-800G-DR8-05 transceiver module is designed for use in 800 Gigabit Ethernet links over 500m single mode fiber. The module has 8 independent electrical input/output channels operating up to 106.25Gbps per channel.

This transceiver consists of two transmitter/receiver units, with each operating on a set of wavelengths on the ITU G.694.2 CWDM at 1310nm.

The transmitter path of the module incorporates a bidirectional PAM4 re-timer ASIC integrated with EML laser and 8-channel internal driver. On the receiver path, used 8 photodiodes and two 4-channel TIA arrays, along with the PAM4 re-timer.

This transceiver is compliant with IEEE P802.3ck, IEEE 802.3cu, OSFP MSA. The built-in digital diagnostics monitoring (DDM) allows access to real-time operating parameters.

## **Key Features -**

- 0 to 500m over SMF with KP4 FEC supported at the Host side

- Dual MPO-12 connector

- Support multi-rate operation

- EML 1310nm transmitter

- PIN and TIA array on the receiver side

- Power consumption < 16W

- Case temperature range: 0°C to 70°C (commercial)

- Safety Certification: TUV/UL/FDA\*1

- RoHS Compliant

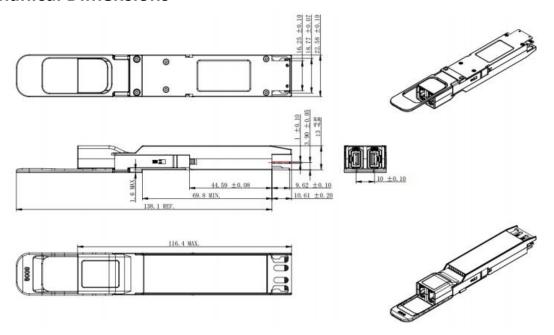

## **Mechanical Dimensions**

The optical interface port is a male Dual MPO-12 connector as specified in IEC 61754-7-1. Mates with two standard type MPO-12 female plug connectors with down-angled interface.

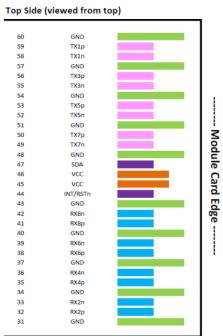

## Pin Assignment -

| Pin# | Logic       | Symbol    | Description                      | Plug Sequence | Notes |

|------|-------------|-----------|----------------------------------|---------------|-------|

| 1    |             | GND       | Ground                           | 1             | 1     |

| 2    | CML-I       | Tx2p      | Transmitter Data Non-Inverted    | 3             |       |

| 3    | CML-I       | Tx2n      | Transmitter Data Inverted        | 3             |       |

| 4    |             | GND       | Ground                           | 1             | 1     |

| 5    | CML-I       | Tx4p      | Transmitter Data Non-Inverted    | 3             |       |

| 6    | CML-I       | Tx4n      | Transmitter Data Inverted        | 3             |       |

| 7    |             | GND       | Ground                           | 1             | 1     |

| 8    | CML-I       | Тх6р      | Transmitter Data Non-Inverted    | 3             |       |

| 9    | CML-I       | Tx6n      | Transmitter Data Inverted        | 3             |       |

| 10   |             | GND       | Ground                           | 1             | 1     |

| 11   | CML-I       | Тх8р      | Transmitter Data Non-Inverted    | 3             |       |

| 12   | CML-I       | Tx8n      | Transmitter Data Inverted        | 3             |       |

| 13   |             | GND       | Ground                           | 1             | 1     |

| 14   | LVCMOS-I/O  | SCL       | 2-wire Serial interface clock    | 3             | 2     |

| 15   |             | VCC       | +3.3V Power                      | 2             |       |

| 16   |             | VCC       | +3.3V Power                      | 2             |       |

| 17   | Multi-Level | LPWn/PRSn | Low-Power Mode/Module<br>Present | 3             |       |

| 18   |             | GND       | Ground                           | 1             | 1     |

| 19   | CML-O       | Rx7n      | Receiver Data Inverted           | 3             |       |

| 20   | CML-O       | Rx7p      | Receiver Data Non-Inverted       | 3             |       |

| 21   |             | GND       | Ground                           | 1             | 1     |

| 22   | CML-O       | Rx5n      | Receiver Data Inverted           | 3             |       |

| 23   | CML-O       | Rx5p      | Receiver Data Non-Inverted       | 3             |       |

| 24   |             | GND       | Ground                           | 1             | 1     |

| 25   | CML-O       | Rx3n      | Receiver Data Inverted           | 3             |       |

| 26   | CML-O       | Rx3p      | Receiver Data Non-Inverted       | 3             | 2 - 5 |

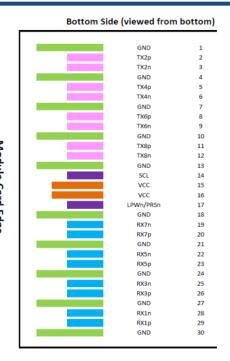

| Pin#     | Logic          | Symbol       | Description                                       | Plug Sequence | Notes |

|----------|----------------|--------------|---------------------------------------------------|---------------|-------|

| 27       |                | GND          | Ground                                            | 1             | 1     |

| 28       | CML-O          | Rx1n         | Receiver Data Inverted                            | 3             |       |

| 29       | CML-O          | Rx1p         | Receiver Data Non-Inverted                        | 3             |       |

| 30       |                | GND          | Ground                                            | 1             | 1     |

| 31       |                | GND          | Ground                                            | 1             | 1     |

| 32       | CML-O          | Rx2p         | Receiver Data Non-Inverted                        | 3             |       |

| 33       | CML-O          | Rx2n         | Receiver Data Inverted                            | 3             |       |

| 34       |                | GND          | Ground                                            | 1             | 1     |

| 35       | CML-O          | Rx4p         | Receiver Data Non-Inverted                        | 3             | _     |

| 36       | CML-O          | Rx4n         | Receiver Data Inverted                            | 3             |       |

| 37       | CIVIE          | GND          | Ground                                            | 1             | 1     |

| 38       | CML-O          | Rx6p         | Receiver Data Non-Inverted                        | 3             | _     |

| 39       | CML-O          | Rx6n         | Receiver Data Inverted                            | 3             |       |

| 40       | CIVIL-O        | GND          | Ground                                            | 1             | 1     |

| -        | CNALO          | _            |                                                   | _             | 1     |

| 41<br>42 | CML-O<br>CML-O | Rx8p<br>Rx8n | Receiver Data Non-Inverted Receiver Data Inverted | 3             |       |

| 42       | CIVIL-O        | GND          | Ground                                            | 1             | 1     |

| 44       | Multi-Level    | INT/RSTn     | Module input/Module Reset                         | 3             | 1     |

| 45       | Tridici Level  | VCC          | +3.3V Power                                       | 2             |       |

| 46       |                | VCC          | +3.3V Power                                       | 2             |       |

| 47       | LVCMOS-I/O     | SCL          | 2-wire Serial interface Data                      | 3             | 2     |

| 48       |                | GND          | Ground                                            | 1             | 1     |

| 49       | CML-I          | Tx7n         | Transmitter Data Inverted                         | 3             |       |

| 50       | CML-I          | Tx7p         | Transmitter Data Non-Inverted                     | 3             |       |

| 51       |                | GND          | Ground                                            | 1             | 1     |

| 52       | CML-I          | Tx5n         | Transmitter Data Inverted                         | 3             |       |

| 53       | CML-I          | Tx5p         | Transmitter Data Non-Inverted                     | 3             |       |

| 54       |                | GND          | Ground                                            | 1             | 1     |

| 55       | CML-I          | Tx3n         | Transmitter Data Inverted                         | 3             |       |

| 56       | CML-I          | Tx3p         | Transmitter Data Non-Inverted                     | 3             |       |

| 57       |                | GND          | Ground                                            | 1             | 1     |

| 58       | CML-I          | Tx1n         | Transmitter Data Inverted                         | 3             |       |

| 59       | CML-I          | Tx1p         | Transmitter Data Non-Inverted                     | 3             |       |

| 60       |                | GND          | Ground                                            | 1             | 1     |

|          |                |              |                                                   |               |       |

#### Notes

- 1. OSFP uses common ground (GND) for all signals and supply (power). All are common within the OSFP module and all module voltages are referenced to this potential unless otherwise noted.

- 2. Open-Drain with pull up resistor on Host.

#### **Control Interface & Memory Map**

The control interface combines dedicated signal lines for LPWn/PRSn, INT/RSTn with two-wire serial (TWS), interface clock (SCL) and data (SDA), signals to provide users rich functionality over an efficient and easily used interface.

#### **SCL** and **SDA**

SCL and SDA are a 2-wire serial interface between the host and module using the I2C or I3C protocols. SCL is defined as the serial interface clock signal and SDA as the serial interface data signal. Both signals are open-drain and require pull-up resistors to +3.3Von the host. The pull-up resistor value shall be 1k ohms to 4.7k ohms depending on capacitive load.

This 2-wire interface supports bus speeds:

Required - I2C Fast-mode (Fm) ≤ 400 kbit/s

- Optional I2C Fast-mode Plus (Fm+) ≤ 1 Mbit/s

- Optional I3C Single Data Rate (SDR) ≤ 12.5 Mbit/s

The host shall default to using 100 kbit/s standard-mode I2C when first accessing an unidentified module for backward compatibility. Once the module has been brought out of reset, the host can read the module's 2-wire interface speed register to determine the maximum supported speed the module allows. For an OSFP, the host may then use I2C Fast-mode, I2C Fast-mode Plus or I3C Single Data Rate, as indicated by the module. It is optional for the host to change the speed of the 2-wire interface but remaining at a low speed could lead to slow management transactions for modules that require frequent accesses.

SCL and SDA signals follow the electrical specifications of Fast-mode, and Fast-mode Plus as defined in the I2C -bus specification or Single Data Rate mode as defined in the Specification for I3C.

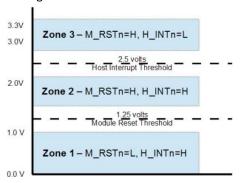

#### INT/RSTn

INT/RSTn is a dual function signal that allows the module to raise an interrupt to the host and also allows the host to reset the module. The circuit shown in OSFP MSA enables multi-level signaling to provide direct signal control in both directions. Reset is an active low signal on the host which is translated to an active-low signal on the module. Interrupt is an active-high signal on the module which gets translated to an active-low signal on the host.

The INT/RSTn signal operates in 3 voltage zones to indicate the state of Reset for the module and Interrupt for the host. Figure 11 shows these 3 zones. The host uses a voltage reference at 2.5 volts to determine the state of the H\_INTn signal and the module uses a voltage reference at 1.25V to determine the state of the M\_RSTn signal.

#### LPWn/PRSn

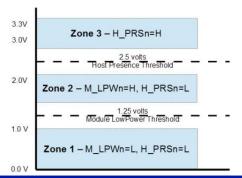

LPWn/PRSn is a dual function signal that allows the host to signal Low Power mode and the module to indicate Module Present. The circuit shown in OSFP MSA enables multi-level signaling to provide direct signal control in both directions. Low Power mode is an active-low signal on the host which gets converted to an active-low signal on the module. Module Present is controlled by a pull-down resistor on the module which gets converted to an active-low logic signal on the host.

The LPWn/PRSn signal operates in 3 voltage zones to indicate the state of Low Power mode for the module and Module Present for the host. Figure 12 shows these 3 zones. The host uses a voltage reference at 2.5 volts to determine the state of the H\_PRSn signal and the module uses a voltage reference at 1.25V to determine the state of the M\_LPWn signal.

#### **SCL and SDA Pin Electrical Characteristics**

| Parameter   | Symbol | Min.    | Тур. | Max.    | Unit |

|-------------|--------|---------|------|---------|------|

| SCL and SDA | VOL    | 0       |      | 0.4     | V    |

|             | VOH    | Vcc-0.5 |      | Vcc+0.3 | V    |

|             | VIL    | -0.3    |      | Vcc*0.3 | V    |

|             | VIH    | Vcc*0.7 |      | Vcc+0.5 | V    |

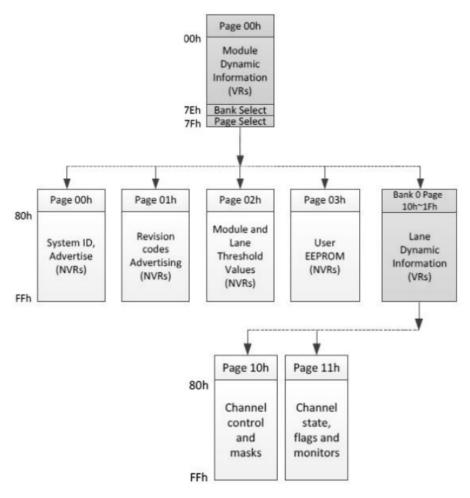

## Memory Map

The control interface and memory map of the OSFP module is compliant with the OSFP MSA. The OSFP module support I2C interface protocol defined by the OSFP MSA. Access clock frequency support a minimum of 100 kHz with no clock stretching and burst read/write of at least 32 bytes.

The module meets the following requirements:

- The module initialize in hardware mode when LPWn is de-asserted.

- The transmitter is disabled when the module is held in reset.

- Tx Squelch function is implemented as defined by the OSFP MSA. When squelched, the transmitter remains on with the modulation turned off.

- Rx Squelch function is implemented as defined by the OSFP MSA. When Rx CDR LOS is asserted, CDR output is squelched.

## **Module Configuration**

#### **Transmitter**

As shown in below figure, the transmitter path of the transceiver contains an 8x25Gbps 2xCAUI-4 electrical input with Equalization (EQ) block, optical multiplexer, DML laser driver, diagnostic monitors and 8 directly modulated laser.

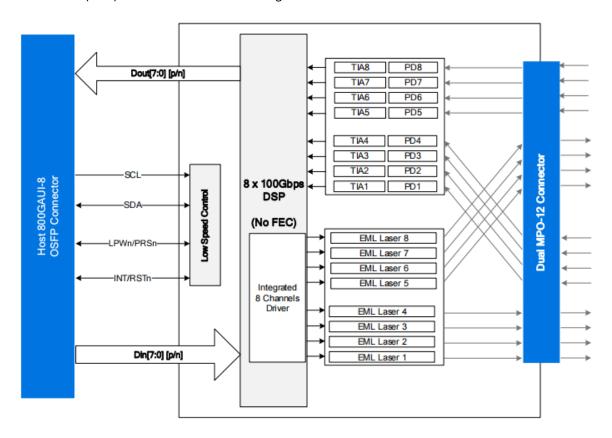

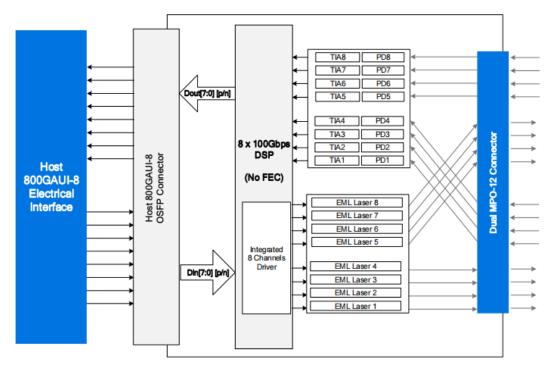

the transmitter path of the transceiver contains an 8x100Gbps 800GAUI-8 electrical input with Equalization (EQ) block, integrated electrical multiplexer, EML laser driver, diagnostic monitors, control and bias for the eight single mode laser source. For module control and interrogation, the control interface (LVTTL compatible) incorporates a Two Wire Serial (TWS) interface of clock and data signals.

#### Receiver

As shown in below figure, the receiver path of the transceiver contains eight PIN photodiodes, trans-impedance amplifiers (TIA), integrated de-multiplexer and 8x100G 800GAUI-8 compliant electrical output blocks. The Rx Output Buffer provides 800GAUI-8 compliant differential outputs for the high speed electrical interface.

#### **Host Speed Electrical Signal Interface**

The interface between OSFP module and ASIC/SerDes is showed in below figure. The high speed signal lines are internally AC-coupled and the electrical inputs are internally terminated to 100 Ohms differential. All transmitter and receiver electrical channels are compliant to module 800GAUI-8 specifications per IEEE 802.3ck.

#### **Control Signal Interface**

The control signal interface is compliant with OSFP MSA. The following pin is provided to control module or display the module status: LPWn/PRSn, INT/RSTn. In addition, there is an industry standard two wire serial interface scaled for 3.3V LVTTL. The definition of control signal interface and the registers of the serial interface memory are defined in the Control Interface & Memory Map section.

#### **Handling and Cleaning**

Exposure to current surges and overvoltage events can cause immediate damage to the transceiver module. Observe the precautions for normal operation of electrostatic discharge sensitive equipment; Attention shall also be paid to limiting transceiver module exposure to conditions beyond those specified in the absolute maximum ratings. Optical connectors include female connectors. These elements will be exposed as long as the cable or port plug is

not inserted. At this time, always pay attention to protection.

Each module is equipped with a port guard plug to protect the optical port. The protective plug shall always be in place whenever the optical fiber is not inserted. Before inserting the optical fiber, it is recommended to clean the end of the optical fiber connector to avoid contamination of the module optical port due to dirty connector. If contamination occurs, use standard MPO port cleaning methods.

## Specifications -

#### **Absolute Maximum Ratings**

Exceeding the absolute maximum ratings table may cause permanent damage to the device. This is just an emphasized rating, and does not involve the functional operation of the device that exceeds the specifications of this technical specification under these or other conditions. Long-term operation under absolute maximum ratings will affect the reliability of the device.

| Parameter                           | Symbol   | Min. | Тур. | Max.    | Unit |

|-------------------------------------|----------|------|------|---------|------|

| Storage Temperature                 | $T_s$    | -40  |      | +85     | °C   |

| 3.3 V Power Supply Voltage          | $V_{cc}$ | -0.5 | 3.3  | 3.6     | V    |

| Data Input Voltage – Single Ended   |          | -0.5 |      | Vcc+0.5 | V    |

| Data Input Voltage – Differential*1 |          |      |      | 8.0     | V    |

| Relative Humidity                   | RH       | 5    |      | 95      | %    |

#### Notes:

1. This is the maximum voltage that can be applied across the differential inputs without damaging the input circuitry. The damage threshold of the module input shall be at least 1600 mV peak to peak differential.

#### Recommended Operating Conditions\*1

For operations beyond the recommended operating conditions, optical and electrical characteristics are not defined, reliability is not implied, and such operations for a long time may damage the module.

| Parameter                                          | Symbol   | Min.  | Тур.   | Max.  | Unit |

|----------------------------------------------------|----------|-------|--------|-------|------|

| Operating Case Temperature*2                       | Tc       | 0     |        | 70    | °C   |

| Storage Temperature                                | $T_s$    | -40   |        | +85   | °C   |

| Power Supply Voltage                               | $V_{cc}$ | 3.135 | 3.3    | 3.465 | V    |

| Operating Relative Humidity                        | RH       |       |        | 65    | %    |

| Power Consumption                                  | $P_D$    |       |        | 16    | W    |

| Electrical Signal Rate per Channel (PAM encoded)*3 |          |       | 53.125 |       | GBd  |

| Optical Signal Rate per Channel (PAM encoded)*4    |          |       | 53.125 |       | GBd  |

| Power Supply Noise*5                               |          |       |        | 66    | mVpp |

| Receiver Differential Data Output Load             |          |       | 100    |       | Ohm  |

| Fiber Length (9um SMF)*6                           |          |       |        | 500   | m    |

#### Notes:

- 1. Power Supply specifications, Instantaneous, sustained and steady state current compliant with OSFP MSA Power Classification.

- 2. The position of case temperature measurement is shown in below figure

- 3. 800GAUI-8 operation with Host generated FEC. The transmitter must receive pre-coded FEC signals from the host ASIC.

- 4. 8×100G DR operation with Host generated FEC. The transmitter must receive pre-coded FEC signals from the host ASIC.

- 5. Power Supply Noise is defined as the peak-to-peak noise amplitude over the frequency range at the host supply side of the power supply filter with the module and filter in place. Voltage levels including peak-to-peak noise are limited to the recommended operating range of the associated power supply. See figure of power supply filter.

- 6. 9μm SMF. The maximum link distance is based on an allocation of 3dB of attenuation and 3dB total connection and splice loss. The loss of a single connection shall not exceed 0.5dB.'

#### **Electrical Characteristics**

Unless otherwise stated, the following characteristics are defined under recommended operating conditions.

| Parameter                               | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------------|--------|------|------|------|------|

| Transceiver Power Consumption           |        |      |      | 16   | W    |

| Transceiver Power Supply Current, Total |        |      |      | 5110 | mA   |

| AC coupling capacitors (Internal)       |        |      | 0.1  |      | uF   |

#### Notes:

1. For control signal timing including LPWn/PRSn, INT/RSTn, SCL and SDA see Control Interface Section.

#### **Reference Points**

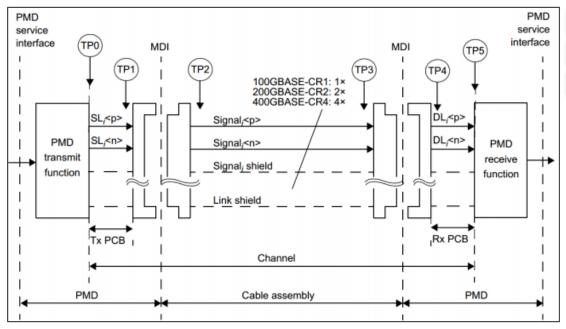

| Symbol                | Description                                                                                                                                                                                                                                                                |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP0 to TP5            | The channel including the transmitter and receiver differential controlled impedance printed circuit board insertion loss and the cable assembly insertion loss.                                                                                                           |

| TP1 to TP4            | All cable assembly measurements are made between TP1 and TP4 as illustrated in IEEE 802.3ck 100GBASE-CR1, 200GBASE-CR2 or 400GBASE-CR4 link figure.                                                                                                                        |

| TPO to TP2 TP3 to TP5 | A mated connector pair has been included in both the transmitter and receiver specifications defined in 802.3ck 162.9.3 and 162.9.4. The recommended maximum insertion loss from TP0 to TP2 or from TP3 to TP5 including the test fixture is provided in 802.3ck 162.9.3.2 |

| TP2                   | Unless specified otherwise, all transmitter measurements defined in 802.3ck 162.9.3 are made at TP2 utilizing the test fixture specified in Annex 162B.                                                                                                                    |

| TP3                   | Unless specified otherwise, all receiver measurements and tests defined in 802.3ck 162.9.4 are made at TP3 utilizing the test fixture specified in Annex 162B.                                                                                                             |

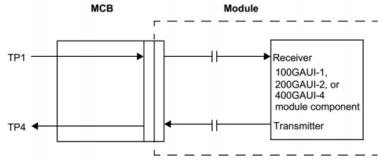

IEEE 802.3ck 100GBASE-CR1, 200GBASE-CR2 or 400GBASE-CR4 link

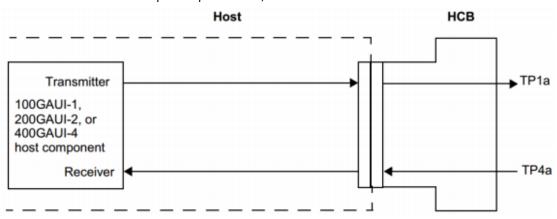

IEEE 802.3ck 400GAUI-4 compliance points TP1a, TP4a

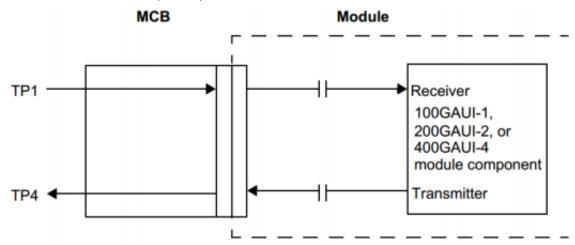

IEEE 802.3ck 400GAUI-4 compliance points TP1, TP4

#### **High Speed Electrical Input Characteristics**

Unless otherwise stated, the following characteristics are defined under recommended operating conditions.

| Parameter                                                                              | Symbol      | Min.              | Тур.              | Max. | Unit      | Conditions  |

|----------------------------------------------------------------------------------------|-------------|-------------------|-------------------|------|-----------|-------------|

| Signaling Rate, Per Lane (PAM4 encoded) Differential Peak-Peak Input Voltage Tolerance | TP1<br>TP1a | 750               | 53.125            |      | GBd<br>mV | +/- 100 ppm |

| AC Common-Mode RMS Voltage Tolerance                                                   | TP1a        | 25                |                   |      |           | mV          |

| Differential-Mode to Common-Mode Return Loss                                           | TP1         | Equation (120G-2) |                   |      |           | dB          |

| Effective Return Loss, ERL                                                             | TP1         | 8.5               |                   |      |           | dB          |

| Differential Termination Mismatch                                                      | TP1         |                   |                   | 10   | %         |             |

| Module Stressed Input Tolerance                                                        | TP1a        |                   | See<br>120G.3.4.3 |      |           | 802.3ck     |

| Single-Ended Voltage Tolerance Range                                                   | TP1a        | -0.4              |                   | 3.3  | V         |             |

| DC Common-Mode Voltage Tolerance Range                                                 | TP1         | -350              |                   | 2850 | mV        |             |

| Module Stressed Input Tolerance Test                                                   |             |                   |                   |      |           |             |

| Pattern Generator Transition Time                                                      |             |                   | 9                 |      | ps        |             |

| Applied Peak-Peak Sinusoidal Jitter                                                    |             |                   | Table 162-16      | 5    |           | 802.3ck     |

| Eye Height                                                                             |             |                   | 10                |      | mV        |             |

| Vertical Eye Closure, VEC                                                              |             | 12                |                   | 12.5 | dB        |             |

| Crosstalk Differential Peak-to-Peak Voltage                                            |             |                   | 845               |      | mV        |             |

| Crosstalk Transition Time                                                              |             |                   | 8.5               |      | ps        |             |

#### **High Speed Electrical Output Characteristics**

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

| Parameter                                                       | Symbol | Min.                 | Тур.                              | Max. | Unit       |

|-----------------------------------------------------------------|--------|----------------------|-----------------------------------|------|------------|

| Signaling Rate, Per Lane (range)                                | TP4    |                      | 53.125 <sup>*1</sup><br>± 100 ppm |      | GBd        |

| AC Common-Mode Output Voltage                                   | TP4    |                      |                                   | 25   | mV         |

| Differential Peak-to-Peak Input Voltage<br>Short Mode Long mode | TP4    |                      |                                   |      | 600<br>845 |

| Eye Height                                                      | TP4    | 15                   |                                   |      |            |

| Vertical Eye Closure                                            | TP4    |                      |                                   |      | 12         |

| Effective Return Loss                                           | TP4    | 8.5                  |                                   |      |            |

| Common-Mode to Differential-Mode Return Loss                    | TP4    | Equation<br>(120G–1) |                                   |      | dB         |

| Differential Termination Mismatch                               | TP4    |                      |                                   | 10   | %          |

| Transition Time                                                 | TP4    | 8.5                  |                                   |      | ps         |

| DC Common-Mode Voltage Tolerance                                | TP4    | -0.35                |                                   | 2.85 | V          |

#### Notes:

1. The signaling rate range is derived from the PMD receiver input.

#### **Optical Characteristics @TP2**

| Parameter Signaling Speed per Lane Modulation Format | Symbol | Min.   | <b>Typ.</b><br>106.25<br>PAM4 | Max.   | <b>Unit</b><br>Gbps |

|------------------------------------------------------|--------|--------|-------------------------------|--------|---------------------|

| Center Wavelength                                    | λ      | 1304.5 | 1311                          | 1317.5 | nm                  |

| Side-Mode Suppression Ratio                          | SMSR   | 30     |                               |        | dB                  |

| Extinction Ratio                                     | ER     | 3.5    |                               |        | dB                  |

| Average Launch Power*1                               |        | -2.9   |                               | 4      | dBm                 |

| OMAouter per Lane                                    |        | -0.8   |                               | 4.2    | dBm                 |

| Launch Power in OMAouter-TDECQ                       |        | -2.2   |                               |        | dBm                 |

| TDECQ (PAM4)                                         |        |        |                               | 3.4    | dB                  |

| RIN21.4 OMA                                          |        |        |                               | -136   | dB/Hz               |

| Average Launch Power of OFF Transmitter              |        |        |                               | -15    | dBm                 |

| Parameter                     | Symbol | Min. | Тур. | Max. | Unit |

|-------------------------------|--------|------|------|------|------|

| Optical Return Loss Tolerance |        |      |      | 21.4 | dB   |

| Transmitter Reflectance       |        |      |      | -26  | dB   |

#### Notes:

1. Average launch power, each lane (min) is informative and not the principal indicator of signal strength. A transmitter with launch power below this value cannot be compliant; however, a value above this does not ensure compliance.

#### **Optical Characteristics @TP3**

| Parameter Signaling Speed per Lane                  | Symbol | Min.   | <b>Typ.</b><br>106.25 | Max.   | <b>Unit</b><br>Gbps |

|-----------------------------------------------------|--------|--------|-----------------------|--------|---------------------|

| Center Wavelength                                   | λ      | 1305.5 | 1311                  | 1317.5 | nm                  |

| Damage Threshold                                    |        | 5      |                       |        | dBm                 |

| Average Receiver Power per Lane                     |        | -5.9   |                       | 4      | dBm                 |

| Saturation Receive Power (OMAouter) per Lane        |        |        |                       | 4.2    | dBm                 |

| Unstressed Receiver Sensitivity (OMAouter) per Lane | Sen*1  |        |                       | -4.4   | dBm                 |

| LOS Assert (Avg.)                                   | Losa   | -15    |                       |        | dBm                 |

| LOS De-Assert (Avg.)                                | Losd   |        |                       | -10    | dBm                 |

| RSSI Accuracy                                       |        | -2     |                       | +2     | dB                  |

| Receiver Reflectance                                |        |        |                       | -26    | dB                  |

#### Notes:

1. Receiver sensitivity (OMAouter), each lane (max) is informative and is defined for a transmitter with TDECQ of 0.9 dB.

#### **Regulatory Compliance Issues**

Various standard and regulations apply to the OSFP-800G-DR8-05 modules. These include eye-safety, Component Recognition, RoHS, ESD, EMC and Immunity. Please note the transmitter module is a Class 1 laser product. See Regulatory Compliance Table for details.

## Regulatory Compliance Table

| reature          |                      |

|------------------|----------------------|

| Laser Eye Safety | y and Equipment Type |

| Testing          |                      |

|                  |                      |

| A<br>TÜVRheinland | Type Approved<br>Safety<br>Regular Production<br>Surveillance |

|-------------------|---------------------------------------------------------------|

| CERTIFIED         | www.tuv.com<br>ID 1419077637                                  |

Component Recognition

**RoHS Compliance**

#### **Test Method**

(IEC) EN 62368-1:2014+A11 (IEC) EN 60825-1:2014 (IEC) EN 60825-2:2004+A1+A2

Underwriters Laboratories (UL) and Canadian Standards Association (CSA) Joint Component Recognition for Information Technology Equipment including Electrical Business Equipment RoHS Directive 2011/65/EU&(EU)2015/863

#### **Performance**

CDRH Accession Number:2132182-000 TUV File: R 50457725 0001 CB File: JPTUV-100513

UL File: E317337

Less than 100 ppm of cadmium. Less than 1000 ppm lead, mercury, hexavalent chromium, poly brominated biphenyls (PPB), poly brominated biphenyl ethers (PBDE), dibutyl phthalate, butyl benzyl phthalate, bis (2-ethylhexyl) phthalate and diisobutyl phthalates.

| Feature                                                           | Test Method                                      | Performance                                                                                                                                                      |

|-------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrostatic Discharge (ESD) to the Electrical Contacts          | JEDEC Human Body Model (HBM)                     | High speed contacts shall<br>withstand 1000V. All other<br>contacts shall withstand<br>2000 V.                                                                   |

| Electrostatic Discharge (ESD) to the Optical Connector Receptacle | IEC 61000-4-2:2008                               | When installed in a properly grounded housing and chassis the units are subjected to 15kV air discharges during operation and 8kV direct discharges to the case. |

| Electromagnetic Interference (EMI)                                | FCC Part 15 Class B;<br>CISPR 32 (EN55032) 2015; | System margins are dependent on customer board and chassis design.                                                                                               |

| Immunity                                                          | IEC 61000-4-3:2010; EN55035:2017                 | Typically shows no measurable effect from a 10V/m field swept from 80 MHz to 6 GHz applied to the module without a chassis enclosure.                            |

#### **Electrostatic Discharge (ESD)**

The OSFP-800G-DR8-05 is complies with the ESD requirements described in the Regulatory Compliance Table. However, in the normal processing and operation of optical transceiver, the following two types of situations need special attention.

Case I: Before inserting the transceiver into the rack meeting the requirements of OSFP compliant cage, ESD preventive measures must be taken to protect the equipment. For example, the grounding wrist strap, workbench and floor should be used wherever the transceiver is handled.

Case II: After the transceiver is installed, the electrostatic discharge outside the chassis of the host equipment shall be within the scope of system level ESD requirements. If the optical interface of the transceiver is exposed outside the host equipment cabinet, the transceiver may be subject to equipment system level ESD requirements.

#### **Electromagnetic Interference (EMI)**

Communication equipment with optical transceivers is usually regulated by FCC in the United States and CENELEC EN55032 (CISPR 32) in Europe. The compliance of OSFP-800G-DR8-05 with these standards is detailed in the regulatory compliance table. The metal shell and shielding design of OSFP-800G-DR8-05 will help equipment designers minimize the equipment level EMI challenges they face.

#### **Flammability**

OSFP-800G-DR8-05 optical transceiver meets UL certification requirements, its constituent materials have heat and corrosion resistance, and the plastic parts meet UL94V-0 requirements.

## Ordering Information

| Product Name | Product Description |

|--------------|---------------------|

|--------------|---------------------|

OSFP-800G-DR8-05 800GBASE-DR8 OSFP PAM4 1310 nm 500 m DOM Dual MPO-12 Connectors, SMF

**Optical Transceiver Module**

## **Contact Information -**

#### **Ascent Communication Technology Ltd**

#### **AUSTRALIA**

140 William Street, Melbourne Victoria 3000, AUSTRALIA Phone: +61-3-8691 2902

#### **CHINA**

Unit 1933, 600 Luban Road 200023, Shanghai, CHINA Phone: +86-21-60232616

#### **EUROPE**

Pfarrer-Bensheimer-Strasse 7a 55129 Mainz, GERMANY Phone: +49 (0) 6136 926 3246

WEB: www.ascentcomtec.com

#### **Hong Kong SAR**

Unit 9, 12<sup>th</sup> Floor, Wing Tuck Commercial Centre 177 Wing Lok Street, Sheung Wan, Hong Kong SAR Phone: +852-2851 4722

#### USA

2710 Thomes Ave Cheyenne, WY 82001, USA Phone: + 1 203 350 9822

#### **VIETNAM**

11th Floor, Hoa Binh Office Tower 106 Hoang Quoc Viet Street, Nghia Do Ward Cau Giay District, Hanoi 10649, VIETNAM Phone: +84-24-37955917

EMAIL: sales@ascentcomtec.com

Specifications and product availability are subject to change without notice. Copyright © 2024 Ascent Communication Technology Limited. All rights reserved. Ver. ACT\_OSFP-800G-DR8-05\_Datasheet\_V1d\_Aug\_2022